**ASICs**

FEB2 V6

CDMR

**Next Steps**

## FEB2 V5.1 for qualification model (camera 1)

#### **Boards available:**

- 313 (315 produced, 2 rejected) => All identical

- Mechanical assembly performed at IRFU on Jan 2020

- New pin added for FEB centering/fixing => in progress => see picture =>

- ~200 boards done on March 30-31

- Upgrade requested after Berlin test (hard to unlock some modules)

- FEBs almost ready for integration in the QM => planned this month

NECTARCAM\_V5.6\_20200302

#### Remote FEB firmware upload

Upgraded to reduce the memory need during upload => pending for validation

#### CDMR documentation data package (available on the NCAM wiki)

- Version 5.1 was the one presented to the CDMR panel as FEB2 V6 performances were not already availabe

- Most of the verifications are now done for FEB2 V6 or in progress showing no major issues so far .

## ASICs for NectarCAM => could be on the critical path

#### Nectar2:

ASIC was initially planned to be produced in Q1 2020 => luckyly, was not the case

- First: some delay due to the covid19 pandemic

- Second: Improvement brought to the chip following similutations (ADC issue)

- Third: Wait for FEB2 V6 tests results (July 2020 –Feb 2021) => just in case ...

- Several issues found during the test: most of them corrected by firmware adjustment and mainly one due to the nectarchip and finally corrected (more details in next slides)

- Nectar2 (+ ACTA with in pulser) submitted to CMP in March 2021=> to be transferred to AMS soon

- Last minute! design correction ongoing (peak in the HG when a trig occured during readout)

- Chips to be packaged by Aptasic (Switzerland)

- we might have some unexpected delay due to the current situation regarding ASIC's market in the world.

#### **Production of PACTA, ACTA, TL0, TL1 ASICs**

- Order sent to IMEC Dec 12 2019

- Total cost: ~188 k€ (as expected)

- Delivery Initially expected by the end of 2020

- Wafers delivered to IMEC in September 2020

- Then sent to ASE

- Side effect of Covid Crisis => huge delay for ASIC Dicing and packaging

- Biweekly follow up with IMEC

- Some information about the CTA project context sent to IMEC 2 weeks ago in order to push for delivery

- Last update (March 30):

- PACTA should be delivered by the end of April but no firm date so far.

- No SODs (ship out dates) for the following ones L0, ACTA and L1.

#### FEB2 V6

#### Reminder => changes requested and consequences

- New Nectar chip with reduced dead time (ping pong mode) => /10

- Firmware updated accordingly

- Reduced memory depth => /2 => 512 cells => 512 ns @ 1 GS/s

- New Nectar Package : QFN 100 instead of QFP 128

- New FEB layout

- Single version of the Nectar chip (top)

- Simplified layout with all 7 Nectar chips on the top side of the PCB (cheaper)

- New clock system => Choice with hard switch between internal and external 66MHz clock

- No more delay lines on the FEB, only L0 ASIC is used, delays adjusted in the DTBP

- No more L1 ASIC required => digital trigger use

#### Intial plan (presented in Barcelona) / reality

Prototype production x 3-5 => early 2020 => March / PCB delivered in May, board delivered end of June 2020 Test and validation => Spring 2020 / July 2020 to February 2021 Small production, 50-60 boards => expected fall 2020 / Pre serial in summer 2021 ?

Software and firmware to be updated (new Nectar, use of ACTA in pulser, reset of IB µController ...)

New firmware available for the Nectar2 chip => current version is : Software updated accordingly, Production test software updated for FEB2 V6

New ACTA chip being produced now, test of in pulser functionality delayed, fw and sw to be updated ...

# FEB2 V6 ping pong (PP) mode debug phase

As usual logbook available on the NectarCAM wiki:

**FEB2 V5**: https://forge.in2p3.fr/projects/nectarcam/wiki/FEB\_V5\_docs\_and\_logbook **FEB2 V6**: https://forge.in2p3.fr/projects/nectarcam/wiki/FEB\_V6\_docs\_and\_logbook

A big thank to all the teams involved who helped during this important phase with a "mention spéciale" to Jean-Luc, Patrick and Eric who worked hard to understand and fix encountered issues.

#### Main issues encountered during the debugging phase:

Peak in the NF scan => Read clk is now running permanently => issue fixed

Acquisition getting stuck with permanent busy

- border effect at specific DT between 2 consecutive trigger

- Firmware improved => issue fixed

LG affected when a trigger occured during readout (only possible in PP mode)

Nectar chip feature => corrected in the design => issue fixed

Bad synchro event =>

improve synchronization process in the firmware => issue fixed

# FEB2 V6 tests summary

#### Stages

- July 2019: New Nectar validated on FEB2 V5 (QFP) with new FW.

- July 2020: FEB2 V6 (with Nectar2 in QFP package) operated in V5 mode => prod test passed (V5 like)

- Fall 2020: Start debug of the ping-pong mode

- Dec 23 2020: FEB V6 firmware stable for PP mode operation

- With expected performances ⇔ FEB2 V5 perfs

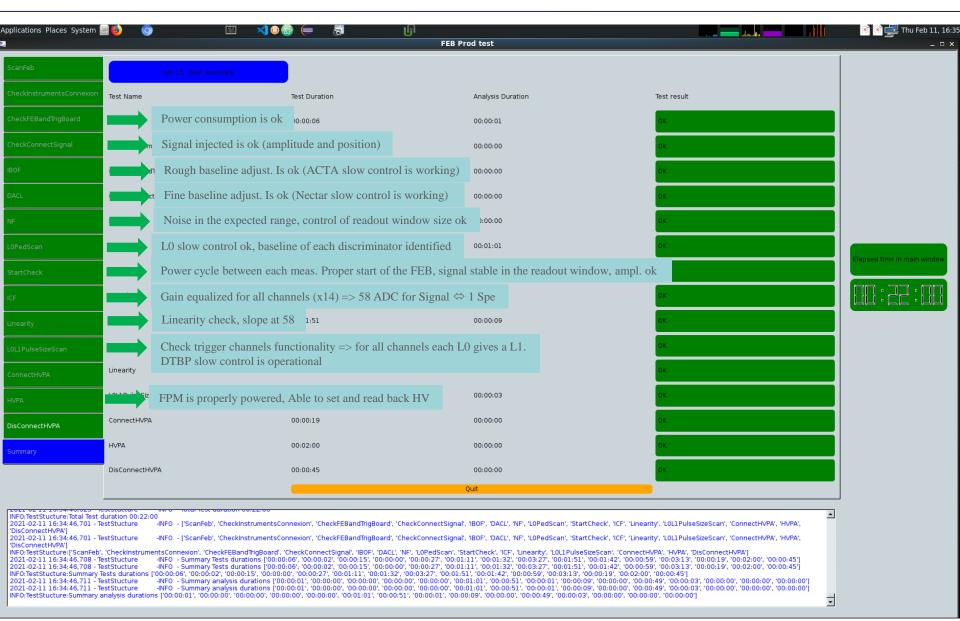

- Jan 2021: prod. test bench upgraded for V6: all tests ok

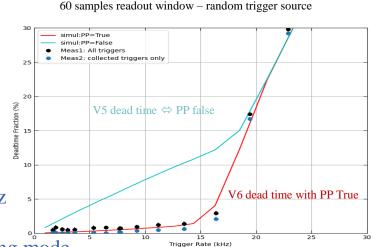

- Jan 27 2021: Deadtime measurement at IRFU with FPM

- DT < 2.5% up to 16kHz

- FEB 11 2021

- Production test ok for FEB2 V6 (x2) operated in ping pong mode

- NEXT STEPS : April 2021

- Validate remaining requirements => ongoing (run taken in March, being analysed)

- Update documents and data package for FEB2 V6

- and still to be done (asap)

- Test of distributed clock configuration (not a requirement)

# FEB2 V6 test summary FEB2 V6 ping pong mode

## CDMR => concerns regarding FEE

### Mainly one concern

## Provide evidence of design verification for FEB V6.

- Already done for most of the FEE requirements (as mentioned during the review)

- Production tests passed in both mode.

- For the 3 remaining reqs (see below) => Specific runs taken at IRFU in March (ongoing analysis, see analysis session)

#### So far, FEB2 V6 is performing as expected and is compliant with FEE requirements

**C-MST-CAM-NC-0152** => Event rate: Digitization dead time

Dead time of digitization and read-out will be < 5% for the nominal CTA trigger

=> Corresponding note: MST-CAM-TN-0331-IRFU: Maximum event rate of NectarCAM

Preliminary measurements give a dead time < 2,5% up to 16 kHz of trigger (random) => Compliant

**C-MST-CAM-NC-0147** dynamic range. The dynamic range of the readout is from 0.5 to 2000 p.e and

C-MST-CAM-NC-0325 non-linearity. The charge non-linearity will be <5% between 0.5 and 2000 p.e.

=> Corresponding note: MST-CAM-TN-0368-IRFU : Linearity of NectarCAM (Crosstalk and B-TEL-1390)

**B-TEL-1380**: Systematic Pixel Timing Uncertainty: The rms uncertainty on the mean relative reconstructed arrival time in every Camera pixel for uniform simultaneous pulsed illumination (<5 ns FWHM) must not exceed 1 ns for amplitudes in the range 20 to 2000 photons per pixel

=> Corresponding note: MST-CAM-TN-0340-IRFU: Timing resolution of NectarCAM

# CDMR => others concerns regarding FEE

# **Nothing critical**

| 42561 | DD034 Ch 11.3. Serial Devices in troubleshoot                                                                | Toussenel Francois | RAMS                  |

|-------|--------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|

|       |                                                                                                              |                    |                       |

| 42399 | DD027-NectarCAM module controller ICD                                                                        | Toussenel Francois | Front End Electronics |

| 42454 | Comments on DD035_NectarCAM NMC Users manual.pdf                                                             | Toussenel François | Front End Electronics |

| 42533 | DD029_ECR_FEB_V5-1toV6: This ECR from the QM to production version has not been implemented in the documents | Toussenel Francois | Front End Electronics |

| 42606 | DD026_LMST-CAM-ICD-0238-LPNHE_FE_BP_interface_v10-2.pdf                                                      | Toussenel François | Front End Electronics |

| 42609 | DD028_I_NCam_Mechanics_FEB_ICD.pdf                                                                           | Toussenel François | Front End Electronics |

| 42761 | DD033 FEB V5.1 performance verification - 7. Firmware / 8. Software                                          | Toussenel François | Front End Electronics |

| 42763 | DD034 NectarCAM Front End Board User Manual                                                                  | Toussenel François | Front End Electronics |

| 42764 | DD034 NectarCAM Front End Board User Manual - 4. Readout System                                              | Toussenel François | Front End Electronics |

| 42766 | DD034 NectarCAM Front End Board User Manual - 8. FEB Initialization                                          | Toussenel François | Front End Electronics |

| 42767 | DD034 NectarCAM Front End Board User Manual - 9. FEB user guide                                              | Toussenel François | Front End Electronics |

| 42768 | DD034 NectarCAM Front End Board User Manual - 11 Annexe 2                                                    | Toussenel François | Front End Electronics |

|       |                                                                                                              |                    |                       |

| 42924 | ICD drawing                                                                                                  | Toussenel Francois | Mechanics and Cooling |

|       |                                                                                                              |                    |                       |

# Documents will be updated along production and test

# Tentative time schedule for the next steps and production

- April 2021: Finalize FEB2 V6 verification according to CDMR request.

- April 2021: FEB2 V6 launch call for offer

- Pre-serial of 25 boards, serial of 1400 boards, option for 1120 boards

- April 2021: Delivery of ASICs by IMEC (PACTA, ACTA, L0, L1)

- Currently worrying: PACTA expected in April, no firm date. No date for other ASICs

- April October 2021: Quality control of the ASICs at ICC-UB

- June 2021: place order for pre serial of 25 boards

- Enough L0 ASICs (100), and current ACTA (no pulser) available

- Pending for Nectar and new ACTA delivery => July 2021?

- July September 2021: delivery of Nectar and ACTA + Quality control of the ASICs

- October 2021: test and validation of pre serial boards in Tower 66

- Includes new ACTA test and validation => Select ACTA version for production

- Pending on ASICs delivery on time

- November 2021: place order for large production of 1400 boards

- Expected rate of 140 boards /month  $=> \sim 1$  year prod.  $=> \sim 2$  months for 1 camera (280 boards)

- Pending for ASICs delivery => produced (IMEC, CMP) and tested (IRFU, ICC-UB)

- December 2022 : End of production